Eletimes

1M

320

Image Credit: Eletimes

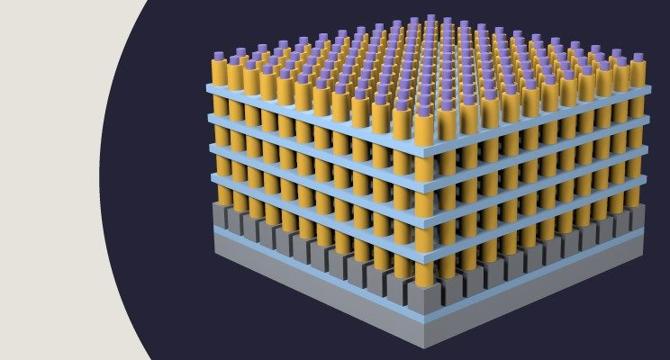

Improving DRAM Performance Using Dual Work-Function Metal Gate (DWMG) Structures

- DRAM technology faces challenges such as gate-induced drain leakage (GIDL) affecting standby charge loss.

- GIDL, caused by band-to-band tunneling under high electric field, escalates off-state leakage currents in DRAM cells, impacting memory retention times.

- Thinner gate oxides and higher doping concentrations exacerbate GIDL, posing a significant issue in low-power, high-density DRAM design.

- Dual work-function metal gate (DWMG) structures show promise in reducing GIDL by controlling the electric field along the channel in DRAM buried word-line (BWL).

- DWMG designs align with industry trends emphasizing advanced gate structures and have been successful in FinFETs and tunnel FETs for leakage reduction.

- Process integration modeling, like SEMulator3D, aids in evaluating DWMG effects by simulating full process flows and analyzing key electrical parameters.

- DWMG simulations reveal reduced current leakage due to a more relaxed electric field distribution and maintained device performance during read and write cycles.

- The combination of device electrical analysis and process integration modeling allows for advanced analyses like electrical pathfinding and variability assessments for optimal designs.

- Future research directions may involve integrating DWMG with high-k dielectrics, assessing scaling trends' impact, and developing predictive models for variability in advanced DRAM nodes.

- Overall, DWMG structures offer scalable solutions to mitigate GIDL in DRAM technology, holding promise for improved performance and reduced leakage currents.

Read Full Article

19 Likes

For uninterrupted reading, download the app